Canali

Ultime news

Ultimi articoli

Le ultime dal Forum |

Correlati TagPassa qui con il mouse e visualizza le istruzioni per utilizzare i tag!

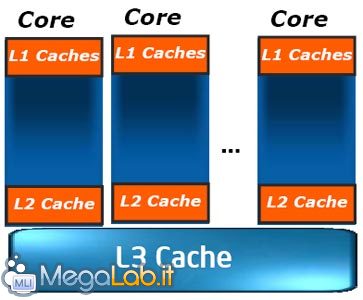

Architettura della cache

Intel ha introdotto importanti novità per quanto riguarda la struttura della cache. Se per la generazione precedente, Penryn, veniva utilizzata una cache L1 per ciascun core e, una cache L2 suddivisa fra tutti i core, ora, con i nuovi Core i7 troviamo un cache L3, ovvero un terzo livello unificato fra i quattro core.

La cache L1 con una grandezza di 64kbytes, suddivisa in due blocchi da 32bytes, presenta tempi di latenza superiori rispetto a quanto accadeva nelle CPU Core 2, essendo passati da tre a quattro cicli di clock. La cache L2 invece, differisce in modo sensibile da quella implementata nelle precedenti soluzioni. Non più unificata fra tutti i core, ma specifica per ognuno di essi. Nel specifico, troviamo una quantitativo pari a 256kbytes, con una latenza pari a 10 cicli di clock dal load, alla fuori uscita dei dati dalla cache. La cache L3 introdotta per la prima volta su processori Intel, è di tipo unificato; Il suo quantitativo è pari a 8mbytes. Tutta via, la cache L3 potrebbe assomigliare alla cache L2 utilizzata nelle CPU Core 2 Quad. Analisi più approfondite però fanno sorgere una sostanziale differenza: nell'architettura Nehalem troviamo una cache L3 unificata tra tutti e quattro i core, mentre nei processori Core 2 quad la cache L2 era suddivisa in due blocchi da 6mbytes ciascuno, i quali venivano associati a una singola coppia di core. Non a caso, nelle schede, che identificano le caratteristiche del processore (in questo caso CPU Core 2 Quad) è possibile trovare la quantità di cache L2 divisa per due (cache L2 = 6x2mbytes). L'architettura della cache integrata in Nehalem, è di tipo inclusivo: Cosa significa? chiariamo questo concetto con un semplice esempio. Nel momento in cui un dato, non è presente nella cache L3, l'architettura inclusiva, fa si che, il suddetto dato non risieda ne nella cache L1 ne tanto meno in quella L2. Di conseguenza la CPU andrà a recuperare quel dato mancante direttamente nel memory controller, evitando passaggi inutili (attraverso le varie cache) che, rallenterebbero il sistema.

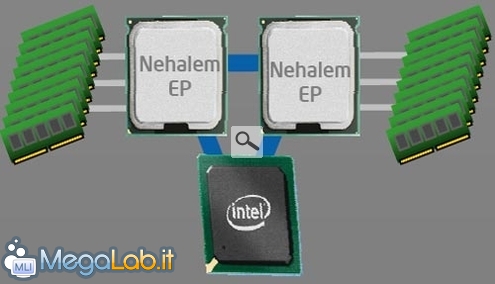

Memory controller integrato

L'ennesimo aspetto interessante, introdotto da Intel nella nuova architettura Nehalem, è senz'altro l'implementazione del memory controller all'interno delle CPU Core i7. Dal canto suo, Intel segue quanto già effettuato dall'acerrimo rivale AMD. Questa soluzione infatti, fu per la prima volta adottata dalla multinazionale con sede a Sunnyvale, introducendo il memory controller all'interno delle CPU destinate al mercato Server. Il memory controller scelto da Intel e, introdotto all'interno delle proprie CPU, è di tipo DDR3 a triplo canale, compatibile con i moduli DDR3 a 1066 MHz e DDR3 a 1333 MHz. Bandwidth massima teorica: 32 GB/s (gigabyte per secondo). Le successive versioni dei processori Core i7, integreranno un memory controller a doppio canale (dual-channel). Scelta giustificata, al fine di ridurre i costi, considerando che questa architettura sarà destinata anche ai segmenti value del mercato informatico. I vantaggi del memory controller integrato non si fermano di certo qui. Intel ha lavorato a finchè le prestazioni migliorassero anche in ambito server. NUMANUMA acronimo di non unifor memory acces, permetterà di accedere al memory controller di altri processori montati sulla stessa scheda madre. Ci riferiamo ovviamente a piattaforme di tipo multi - socket. L'accesso ai dati nel memory controller di un altro processore, avverà con un impatto prestazionale in termini di bandwidth e latenza. Il trade off potrà però, essere ridotto, grazie a future applicazioni specificatamente sviluppate per l'architettura NUMA.

QuickPath Interconnect

Con la nuova architettura Nehalem, Intel introduce un nuovo bus di collegamento tra processore, chipset e memory controller. Stiamo parlando del nuovo QuickPath Interconnect, il sostituto della oramai vecchia architettura Front Side Bus, meglio conosciuta come FSB. Con il nuovo bus di connessione, di tipo point to point si raggiungono velocità teoriche di 12.5 gbps. Il limite, sempre teorico, di trasferimento sui link bidirezionali è attestato intorno ai 25 gbps. In futuro Intel potrebbe incrementare la velocità di trasferimento dati tramite QPI, alzando le frequenze di trasmissione di quest'ultimo. Come accaduto per i memory controller integrato, Intel segue un approccio molto simile a quello adottato da AMD con il suo bus di connessione denominato HyperTransport. Data quindi la somiglianza fra le due tipologie di connessione, il bus QPI, rappresenterà per Intel un indubbio vantaggio unito alla nuova architettura Nehalem, soprattutto in ottica server.

Istruzioni SSE 4.2

All'interno dei nuovi processori Core i7, Intel ha introdotto un nuovo set di istruzioni appartenenti alla famiglia SSE. In Nehalem, queste istruzioni giungono alla versione 4.2.. Attualmente, non esistono applicazioni in grado di sfruttare le potenzialità offerte dalle nuove istruzioni. Turbo Mode e consumi Architettura dell'engine e Hyper Threading Pagine

Segnala ad un amico |

- Unisciti a noi

- | Condizioni d'uso

- | Informativa privacy

- | La Redazione

- | Info

- | Pressroom

- | Contattaci

© Copyright 2025 BlazeMedia srl - P. IVA 14742231005

- Gen. pagina: 1.16 sec.

- | Utenti conn.: 425

- | Revisione 2.0.1

- | Numero query: 45

- | Tempo totale query: 0.18